Professional Experience

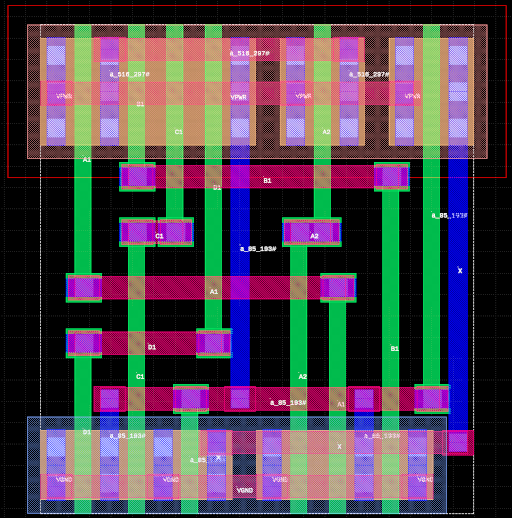

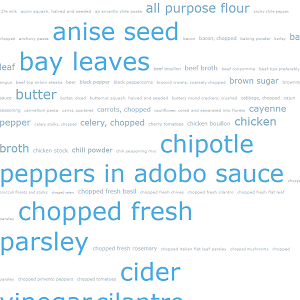

Broccoli [webbroccolimicro.io]

Founder

Developed the key Intellectual Property for the first product, developed a course on self timed circuits to bootstrap the hiring pipeline, developed a thorough value proposition through in-depth market research, wrote a grant to the NSF Seed Fund, developed a full three statement financial model to project viability of the business, and continuous networking for customer relationship and customer product validation.

Bloomington, IN

Dec 2021 - Current

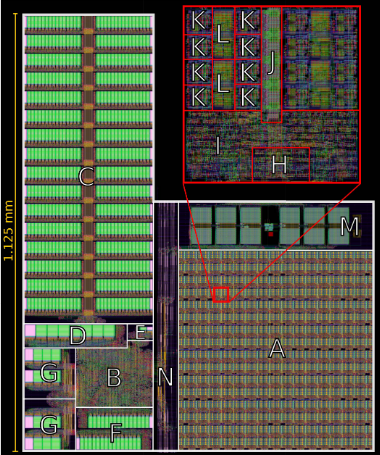

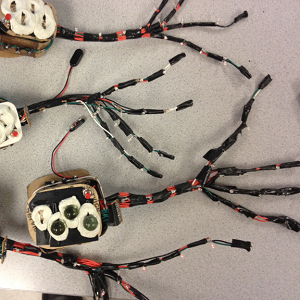

JRC Integrated Systems

Senior Microelectronic Design and Test Engineer

Bloomington, IN

Feb 2024 - July 2024

Siden

Principal Backend Engineer

Mentored and managed six team members. Three were promoted to leadership roles and are now managing small teams while owning and developing major subsystems of the product. Designed, and implemented a system for routing user requests in a large scale Content Distribution Network (CDN), a major feature required for final product functionality. Deployed the staging and production clusters with a cross-functional team finalizing the product allowing the rest of the engineering org to push updates to production through CI/CD processes.